Home > Products > PowerBaum

PowerBaum

PowerBaum provides fast and accurate power models to enable system-level power analysis for an entire system-on-chip (SoC) with realistic scenarios

Home > Products > PowerBaum

PowerBaum provides fast and accurate power models to enable system-level power analysis for an entire system-on-chip (SoC) with realistic scenarios

PowerBaum automatically generates fast, yet very accurate, power models that plug easily into a variety of third-party EDA tools such as HDL and ESL simulators. It enables system-level power analysis for an entire SoC with realistic scenarios, which is impossible with other currently available technologies today.

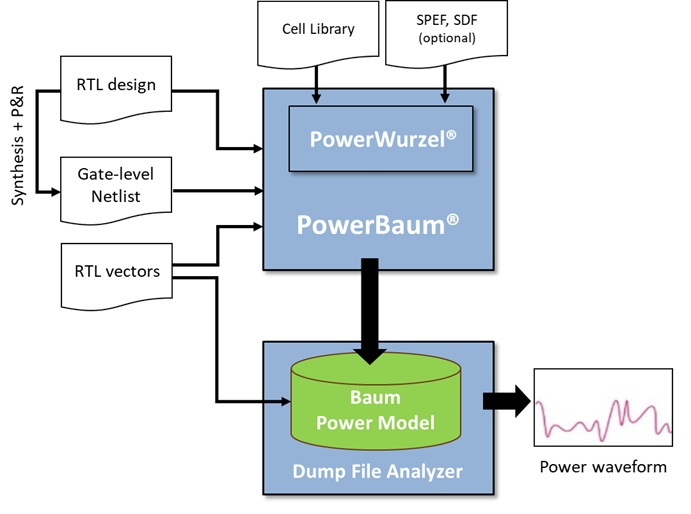

PowerBaum takes RTL (Verilog) designs, a cell library, gate-level netlists (Verilog), and switching information (FSDB or VCD). It automatically generates a high-level power model of the given design in Baum’s proprietary binary format. The power model is then linked with a commercial RTL or ESL simulator (e.g., Synopsys VCS and Platform Architect). While the RTL or ESL simulator runs, it generates power waveforms on-the-fly.

Step 1: Provide input collaterals (RTL design & vectors, netlist, library, SPEF)

Step 2: Train power model

Step 3: Run power analysis using Baum’s power model

Power bugs are undesirable power consumption in your design. Power debugging requires users to analyze billions of clock cycles running different mode of operations to consider different scenarios (e.g. IP turning on/off, when one of sub-system is idle) to spot if there is any power bug lurking in the power profile.

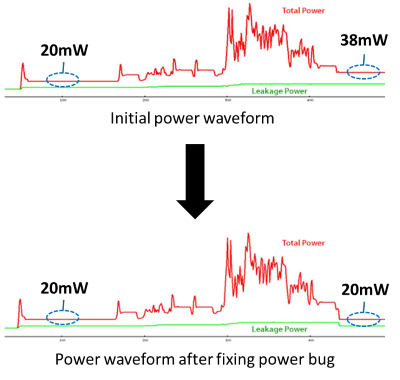

PowerBaum’s power models run orders of magnitude (100x) faster compared to competing technologies while maintaining gate-level power accuracy giving users the best of both words. This allow users to run system level simulation with realistic workloads and generate power profile of billions of clock cycles which later can be analyzed for power debugging. With dynamic power analysis capabilities (analyzing the power waveform), users can easily zero in on the exact parts of the design that are consuming excess power and fix it as illustrated in the figure.

Power doubled vs previous idle state (20mW)

Fixed critical power bug

Power reduced by 47%

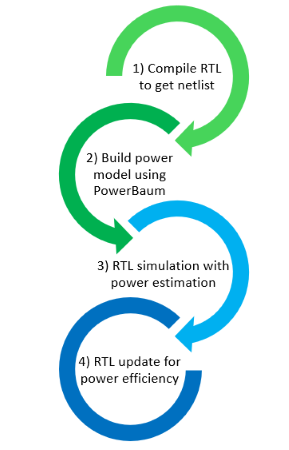

Early power-related design decisions have the most potential to minimize power consumption in a semiconductor design. Integration of PowerBaum into RTL simulation is very easily making it very feasible for RTL optimization. Therefore, RTL designers working on a variety of semiconductor designs, ranging from data centers and CPUs to automotive ICs, can use PowerBaum to analyze and minimize power consumption in the early design stage for the highest impact.

PowerBaum’s fast power analysis capabilities can perform whole flow with batch process within a day – several orders of magnitude faster than current competitors.

Software/Hardware Power Profiling

System architectures of today’s designs employ much more hardware and software interaction than in the past. Software power management plays a key role in managing the power and thermal characteristics of a system. In addition, the activity levels of software running on a device play a key role in the overall power consumption.

Yet existing solutions in the market today don’t provide designers a means to analyze power accurately with realistic software scenarios. This prevents them from truly understanding if their power management routines are doing their job correctly or to understand the power and thermal effects of software activity on their designs.

PowerBaum’s power models provide both the speed and accuracy to run realistic software loads on the entire design enabling designers to understand the hardware/software interaction as it relates to power consumption and thermal efficiency. In addition, PowerBaum’s power models integrate into ESL simulation environments allowing designers to easily run their software and analyze and optimize power.

Power Sign-off

Power sign-off prior to tape out has been a near impossibility with existing solutions in the market. Because existing power analysis solutions are much too slow to run realistic scenarios, designers struggled to prove their designs will meet the power budget under a real load. Running a very small slice of a scenario with just a piece of the design does not validate power for sign-off but, unfortunately, this is only what existing solutions are capable of.

PowerBaum power models combine the speed and accuracy required to break through these barriers for power sign-off. They run 100x faster than existing solutions allowing designers to run realistic scenarios (real loads) with very high accuracy. In addition, PowerBaum’s technology has a much higher capacity than existing solutions in the market allowing users to analyze the power for their whole design. Now users can use PowerBaum’s power models in power sign-off before tape-out and have confidence that their design will meet its power budget.

AI Chip Design

In the case of AI inference processors, designers are in a continuous struggle to improve the performance of the processor. Since battery technology has been stagnant, designers are forced to reduce the power of their inference processors. Besides, the ever-developing machine learning algorithms necessitate analyzing design’s power weekly and often daily.

PowerBaum provides the both speed and accuracy required by AI chip designers to optimize their design. A single power model generated by PowerBaum can be utilized to do power analysis with multiple PE (Processing Elements) instances giving designers the freedom to optimize the power

consumption of AI chips

Power and Performance Tradeoffs

Power, performance, and area are the three axis of design architecture. Trading off and optimizing each are key to a product’s success and marketability. Techniques for optimizing area are relatively straightforward and well understood. Optimizing performance is typically done early in the design cycle at the architectural or micro-architectural level. Optimizing power has always been difficult; there is really no methodology that allows architects and designers to accurately optimize power while they are making performance trade-offs. Existing power analysis solutions are either too slow, applied too late in the design cycle, are not accurate, or cannot be automated. Their limited capabilities are huge barriers to easily and accurately provide a power/performance methodology allowing designers and architects to understand and optimize the trade-offs between the two.

PowerBaum’s power models are the answer. They maintain the required implementation accuracy for power analysis to be congruent with the performance analysis while, at the same time, accelerate power analysis speeds by orders of magnitude (100X) compared to existing solutions. Now architects and designers can make true power performance tradeoffs running realistic scenarios, under realistic software loads. They can make changes in the design to increase performance and immediately understand the effects of the changes on power consumption.

IP Power Modeling

IP companies have always struggled creating and delivering accurate power models to their customers, who desperately need them to validate and optimize their SoCs. This is because there has been no way to automatically create accurate models for IPs in a secure and portable manner. Lack of validated models from IP vendors have led designers to rely on various ad hoc methods to analyze and optimize the power of their designs. This has created a huge gap in their methodology and added undo risk to their projects.

PowerBaum answers this need by providing a methodology for IP providers to automatically create power models for their IPs. These models are very fast and accurate (implementation accurate) and, most importantly to IP providers, they are very portable and secure. IP providers can rely on PowerBaum solutions to quickly create power models of their IPs through an automated flow and deliver these models securely to their customers. The IP power models are portable and can be used in any simulation environment (RTL simulation, ESL/Virtual Platform simulation, or emulation).

Using PowerBaum power models for 3rd party IP closes the methodology gap in analyzing and optimizing power for the end user and creates confidence with the designers that the 3rd party IP is meeting its power budgets.

IR Drop Analysis

Ensuring the integrity of the power distribution network of a device is one of the key components in design closure. As process dimensions shrink with faster switching frequencies they induce much higher switching currents in the power networks. In addition, shrinking device dimensions cause higher resistance in the networks and interconnects. This increase in current and resistance makes todays devices much more vulnerable to IR drop in the power grid causing the device to run slower, increasing noise, and reducing operating margins. Increasing noise in the device can often lead to device failures. A robust power distribution network is key to reliable operation of the device in high-performance designs.

IR drop analysis is key to ensuring the reliable operation of the chip. IR drop analysis tools in the market rely on the designer to understand and apply peak power scenarios for the analysis input. Peak power is either estimated or modeled from very short simulations and so risk missing real peak power behavior. Designers need the capability to run real loads on the device to really understand the peak power conditions. Unfortunately, existing tools in the market are too slow to run realistic loads on the device. That was certainly true until PowerBaum came along.

Now with PowerBaum power models, designers can understand peak power constraints from realistic scenarios and workloads. These peak power parameters can then be fed back as inputs to the IR power analysis tools for a better and more realistic IR drop understanding resulting in a more robust and reliable power grid design.