PowerSpion Features

- Super fast and lightweight tailored for RTL CI/CD

- Automatically extract ICGs from RTL structure and compute various clock gating metrics (CGR, CGE, ICGE)

- Power-proxy waveform that provides power pattern insights (e.g. peak power region)

- Clock gating linting

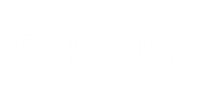

How PowerSpion Works

PowerSpion automatically extracts clock gating structure from RTL design and reports clock-gating metrics (e.g. CGR, CGE, ICGE) without running computation-expensive power estimation.

Once RTL vectors (FSDB or VCD) are prepared, user can run PowerSpion to generate clock-gating metrics based on both instantiated and inferred ICGs from RTL design to generate clock-gating metrics reports as well as power-proxy waveforms.

If RTL vectors are not available in the early stage, users can perform vectorless clock-gating analysis to estimate CGE until a testbench becomes available.

Infer ICGs from RTL design

Super fast clock-gating analysis

Vectorless clock-gating analysis

ACR Waveform

ACR (Active Clock Ratio) is defined as the percentage of flip-flops whose gated clock remains active during each clock cycle.

The figure illustrates that the ACR waveform shows strong correlation with the gate-level power profile. This metric proves valuable in guiding power-aware RTL development, particularly in scenarios where dynamic power constitutes a significant portion of the total power, such as in advanced technology nodes and data-intensive applications.

ACR waveform can be used to narrow-down time windows that are most likely to exhibit peak power.

Clock Gating Linting

PowerSpion conducts thorough checks on RTL designs, detecting any erroneous usage of clock gating without requiring vectors. Following are some of the cases we support.

- Constant ICG

- Floating ICG

- Redundant cascaded ICG

- Memory w/o ICG

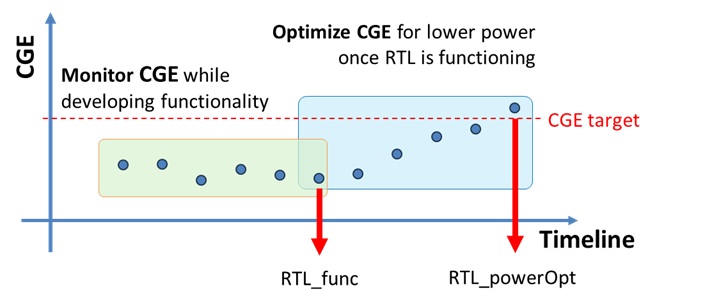

RTL CI/CD Pipeline

Users can facilitate power-aware RTL development by seamlessly integrating PowerSpion into RTL CI/CD pipeline.

RTL engineers can track the progress of clock-gating metrics throughout the development cycle to strengthen their confidence in power quality of their design.

Team lead leverage this data to drive power-aware RTL sign-off.